图1 DDS模型

付扬

(北京工商大学 计算机与信息工程学院, 北京 100048)

摘要:针对模拟信号源存在精度低、频率范围小,以及定制直接数字频率合成信号源的控制方式、置频速率等不满足系统要求的问题,设计了一种基于FPGA的信号源。该信号源基于直接数字频率合成原理,采用FPGA的模块化设计方法, 实现了频率、相位、幅值可调的正弦波、方波、三角波等波形输出。实验表明,该信号源输出波形质量好,频率分辨率高,控制灵活、方便。

关键词:信号源; 现场可编程门阵列; 直接数字频率合成

网络出版地址:http://www.cnki.net/kcms/detail/32.1627.TP.20160705.1502.014.html

信号源在产品研发及生产实践中有广泛的应用。模拟信号源便于集成,操作简单,且频谱纯度较高,使用比较广泛,但精度较低,频率范围小,存在高分辨率和快转换速度之间的矛盾,因此需要研发高性能的信号源。直接数字频率合成(Direct Digital Frequency Synthesis,DDFS,简称DDS)是从相位概念出发,直接合成所需波形的一种新的频率合成技术,与传统的模拟式波形产生法相比,具有频率转换速度快、频率分辨率高、相位噪声小、频率稳定度高、集成度高、易于调整及控制灵活等优点。但目前已有的定制DDS芯片在控制方式、置频速率等方面常常与信号发生、通信、雷达等系统的要求差距很大,且不能实现修改。

现场可编程门阵列(Field-Programmable Gate Array,FPGA)是在可编程器件基础上发展而来的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。FPGA具有规模大、速度快、编程修改方便、应用灵活等优势,同时具有强大的软件支持,其发展使设计满足自行需要的高性能DDS信号源成为可能[1]。

FPGA的设计开发软件Quartus II实现了硬件设计的软件化。其模块的功能仿真避免了直接硬件设计不合适所带来的时间和成本浪费,使设计易于开发、修改灵活快捷。其内嵌入式逻辑分析器SignalTap II是系统级的调试工具,进一步降低了系统的硬件设计难度,满足FPGA开发中硬件调试的要求,对最终系统实现的验证具有实时性和可视性,减少了传统调试验证的时间,加快了设计周期。因此,笔者采用FPGA和DDS技术设计了一种信号源,其具有可编程、数字化、速度快、分辨率高等特点。

1.1 设计原理

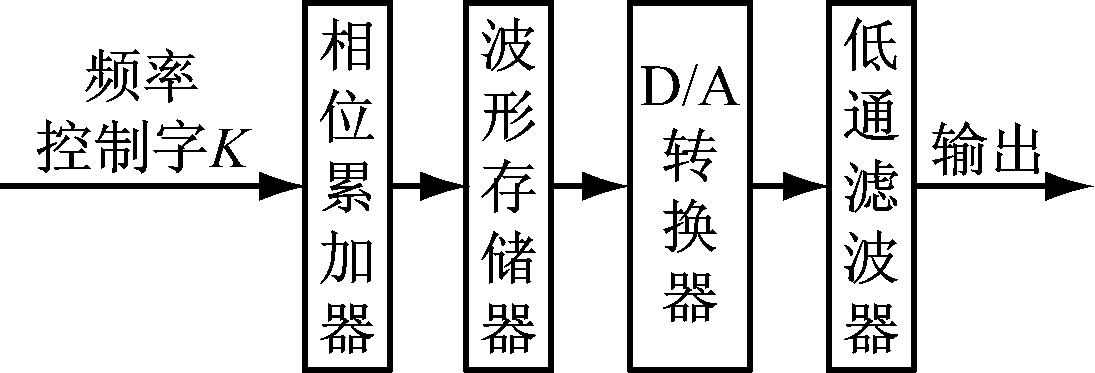

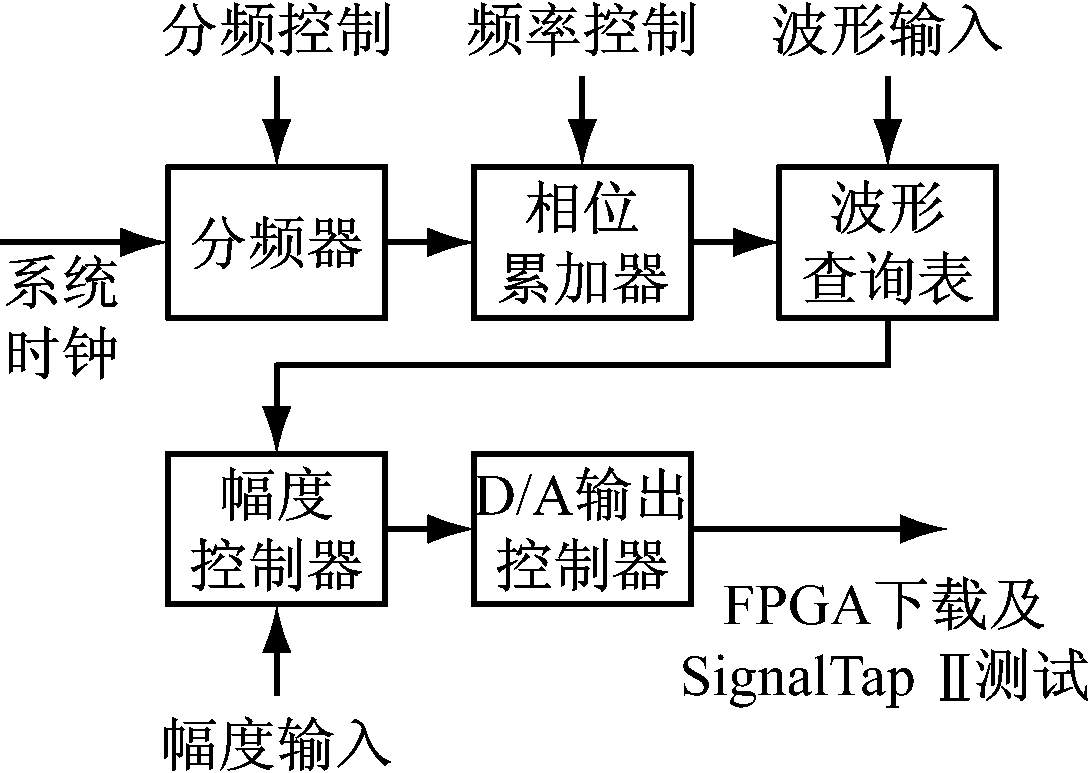

信号源的设计依据DDS原理[2]。DDS模型由相位累加器、波形存储器、D/A转换器及低通滤波器构成,如图1所示。

图1 DDS模型

相位累加器是决定DDS性能的关键部分。相位累加器的位数直接影响输出信号的频率调节范围、频率分辨率、相位差的调节范围及相位差的分辨率。相位累加器由N位加法器与N位累加寄存器构成。每来1个时钟脉冲,加法器将频率控制字K与累加寄存器输出的累加相位数据相加,将相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字K相加。相位累加器在时钟作用下,不断对频率控制字K进行线性相位累加。由此可看出,相位累加器在每一个脉冲输入时,将频率控制字K累加1次,相位累加器输出的数据即合成信号的相位,相位累加器的输出频率即DDS输出的信号频率[3]。

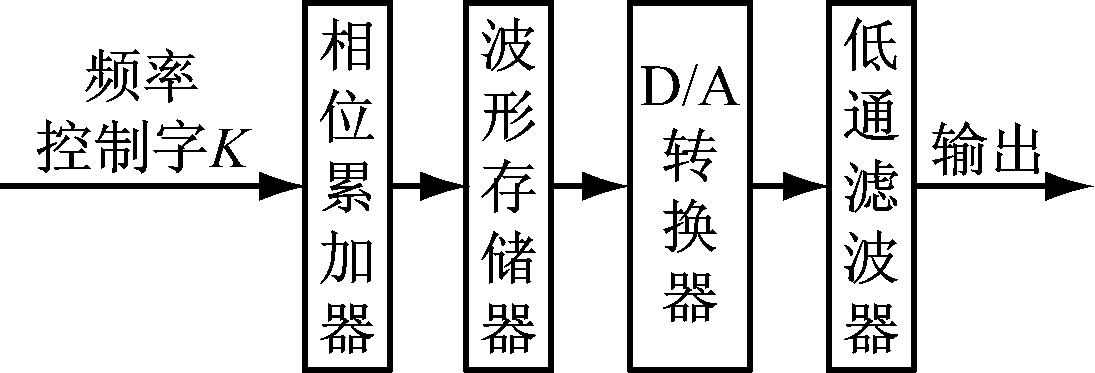

图2为4位累加器(N=4)原理。其中A1—A4,B1—B4为4位加法器的输入,W1—W4为加法器的输出;4位累加寄存器由4位D触发器构成,D1—D4为其输入,CP为时钟脉冲,Q1—Q4为其输出。

对累加寄存器而言,其输入等于加法器的输出,即D4D3D2D1=W4W3W2W1。

图2 4位累加器原理

累加寄存器的输出为加法器的输入,即Q4Q3Q2Q1=B4B3B2B1。

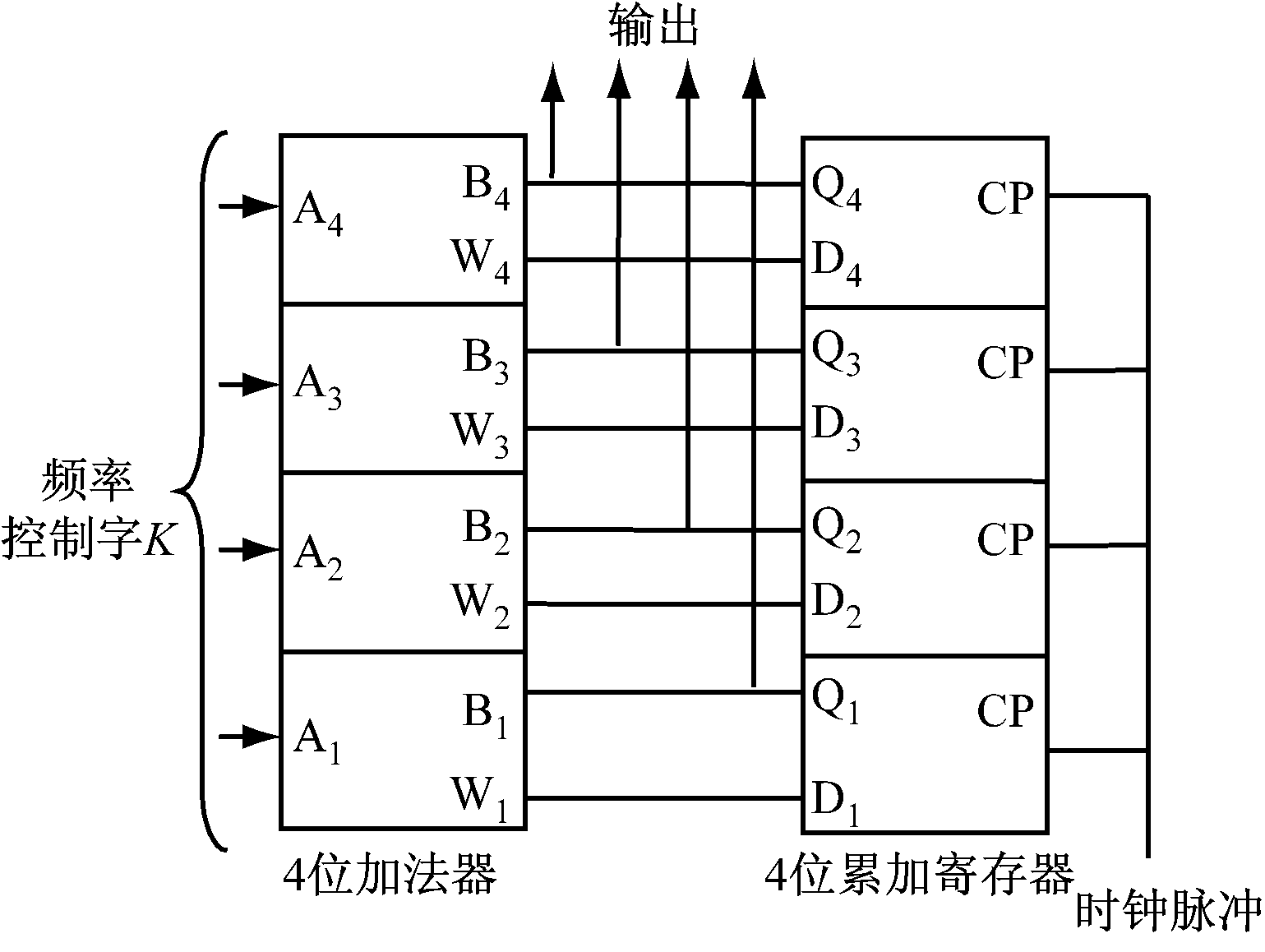

设频率控制字K为A4A3A2A1=0001,且累加器电路输出初态为Q4Q3Q2Q1=0000,则在时钟脉冲的作用下,电路的状态转换如图3所示。可看出电路共有16个状态,相位输出以16个时钟脉冲为周期,相位增量M=0001。

图3 A4A3A2A1=0001时的电路状态转换

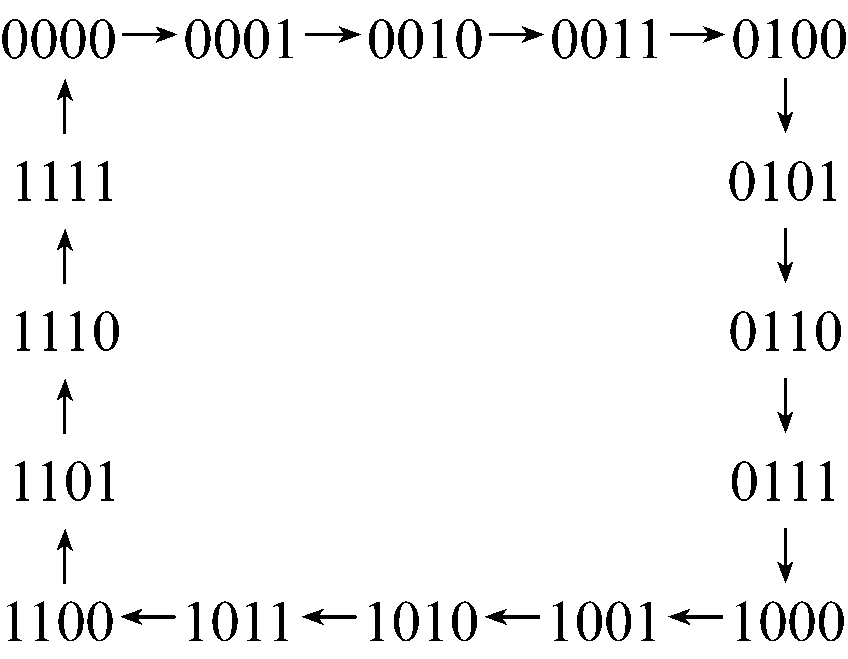

电路输出初态为Q4Q3Q2Q1=0000时,若频率控制字K为A4A3A2A1=0010,则电路状态转换如图4所示。可看出电路共有8个状态,相位输出以8个时钟脉冲为周期,相位增量M=0010。

图4 A4A3A2A1=0010时的电路状态转换

依次类推,可见频率控制字K既控制了相码增量值,即DDS模型输出每个波形的采样点数,又控制了输出信号的频率。若相位累加器为N位,则有

(1)

(2)

式中:f0为DDS输出信号频率;fclk为参考时钟脉冲频率。

采样点数为2N/M。若fclk一定,则f0越大,采样点数越少。最小步进为fclk/2N,频率达到最小步进值时,采样点数最多。设计时根据所要求的最高频率和最少采样点数可确定fclk,根据最小步进和fclk可确定N,根据最高输出频率和最小步进可确定M。DDS频率分辨率为fclk/2N,也可以用累加器位数N表示,若fclk一定,则N越大,频率分辨率越高。

用相位累加器输出的数据作为波形存储器的相位取样地址,即可将存储在波形存储器内的波形抽样值经查找表查出。波形存储器的输出送至D/A转换器,D/A转换器将数字量形式的波形幅值转换为模拟量信号[4]。

1.2 设计方案

信号源采用FPGA模块化设计,由分频器、相位累加器、波形查询表、幅度控制器及D/A输出控制器组成[5],如图5所示。分频器为信号源提供基准时钟;相位累加器对频率控制字进行累加,决定输出信号的频率和相位,累加结果作为波形查询表的下一个取样地址;波形查询表存储各种波形数据;幅度控制器控制输出信号的幅度;D/A输出控制器的输入即为波形查询表和幅度控制器的输出,其输出信号下载到FPGA芯片CycloneⅡ EP2C35F672C8进行SignalTapⅡ仿真测试。信号源各模块采用VHDL语言设计,顶层采用图形法设计。

图5 信号源组成

设计的信号源产生0~160 kHz、频率最小步进为5 Hz的波形信号。根据式(1)、式(2)可计算出fclk,N,M。若f0达到160 kHz,采样点数为64,则fclk不小于10.24 MHz。为实现5 Hz的频率最小步进,此时采样点数最多,由5=fclk/2N得N=21,即相位累加器为21位,最终输出信号频率f0与相位增量M的关系为f0=5M。由于f0最大值为160 kHz,则M≥32 000,而215=32 768,所以选择相位增量的最低位数为15位。

根据设计方案,信号源各模块采用VHDL硬件描述语言编程设计[6-7],在QuartusⅡ环境下进行编译、仿真和调试后,生成器件模块。采用图形法调用各模块设计信号源系统顶层,包括分频器、相位累加器、查询表、幅度控制器、D/A输出控制器5个模块。

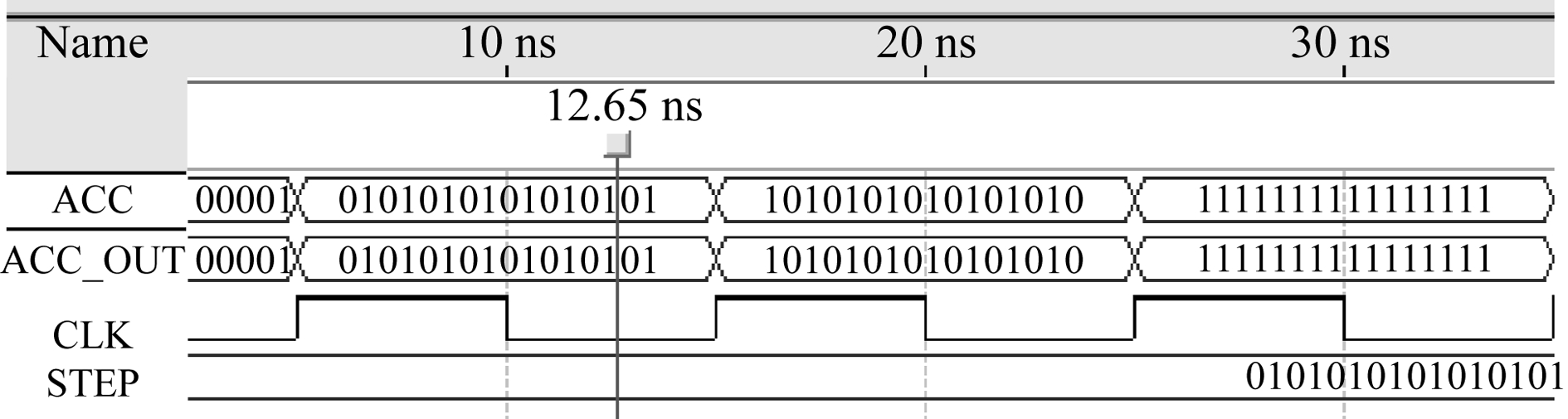

对相位累加器模块进行VHDL编程时,设CLK为系统时钟,STEP为频率控制字输入,ACC为中间定义信号,ACC_OUT为模块输出。对相位累加器模块进行功能仿真,结果如图6所示,可看出在每个CLK的上升沿,相位累加器以STEP为基本单位进行累加。

图6 相位累加器模块功能仿真结果

查询表模块用于存储各种波形数据,对相位累加器送入的数据进行查询。设置该模块波形选择输入变量CHOICE为2位二进制数,分别为00,01,10。当CHOICE为00时,查表得到正弦波;当CHOICE为01时,查表得到方波; 当CHOICE为10时,查表得到三角波。

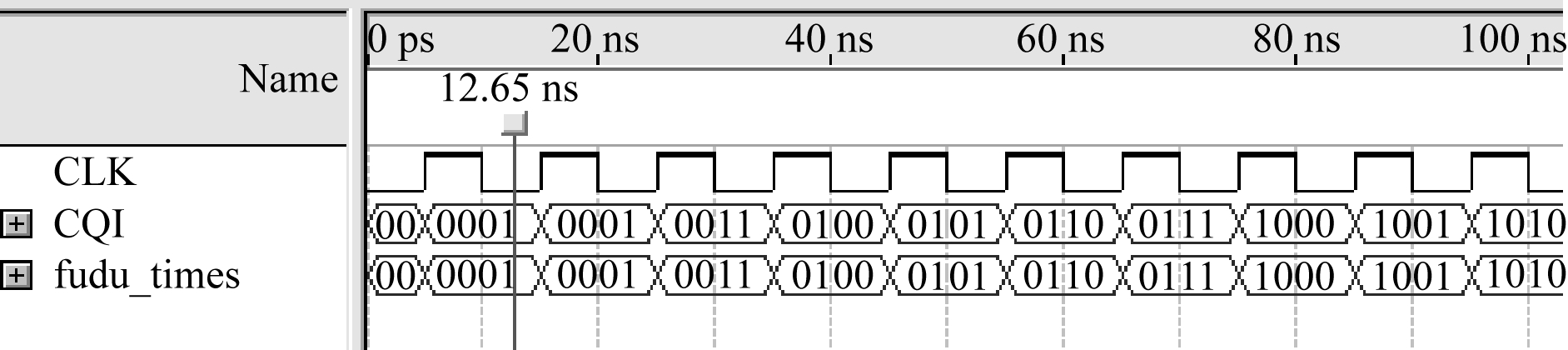

幅度控制器模块用于控制输出波形的幅度,设CLK为该模块的时钟信号,CQI为VHDL编程时的中间变量,fudu_times为模块输出。仿真结果如图7所示,可见在CLK每一个上升沿,fudu_times加1。

图7 幅度控制器模块仿真结果

采用CycloneⅡ EP2C35F672C8型FPGA芯片。该芯片集成了33 216个逻辑单元(约165万门)和473 kB片上RAM,拥有672个引脚,速度等级为8级。在QuartusⅡ软件中,将设计的输入、输出进行芯片引脚锁定,完成编译。在QuartusⅡ的SignalTapⅡ逻辑分析仪界面进行时钟锁定、引脚锁定及硬件连接;在SOF Manager中添加要测试的.sof文件,并进行硬件下载[8]。文件下载后,进行SignalTapⅡ仿真测试,设定频率步进STEP为F500H,时钟控制信号CLK_SEL为1,幅度输出amplitude_times为FH,波形选择信号CHOICE为00,01,10,波形输出信号为DOUT,得到信号源输出仿真波形如图8所示。

从图8可看出,当CHOICE为00时,信号源输出正弦波;当CHOICE为01时,信号源输出方波;当CHOICE为10时,信号源输出三角波。仿真结果验证了设计方案的正确性。

图8 信号源输出仿真波形

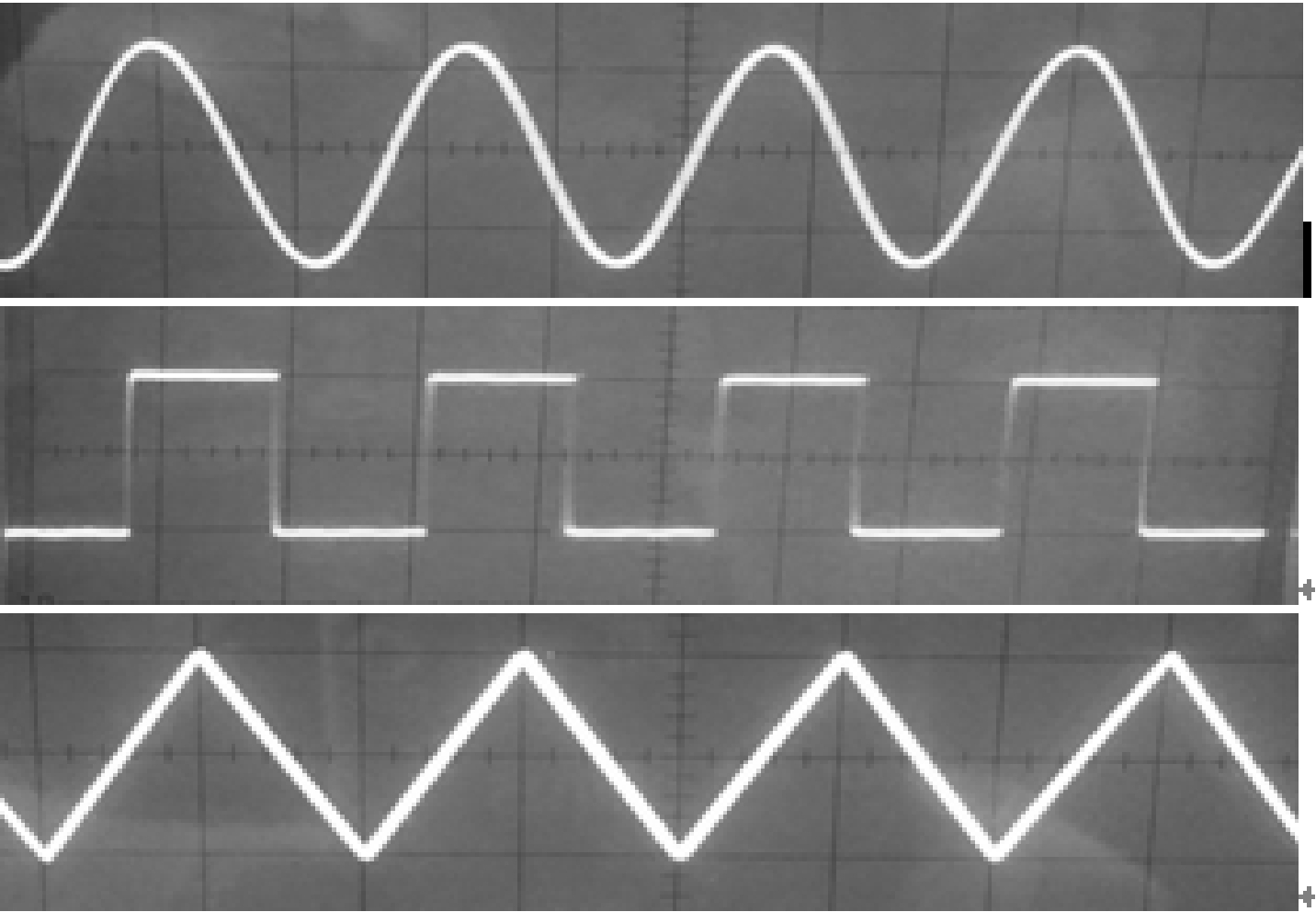

采用示波器对信号源进行测试,测试波形如图9所示,自上而下依次为CHOICE为00,01,10时的输出波形。可见信号源输出波形与仿真结果一致。

图9 信号源测试波形

依托FPGA技术的软件编程、编译、仿真和测试的强大支持,以及FPGA具有的高密度、可编程和在线下载等特点,实现了根据需要自行设计的高性能和数字化DDS信号源,克服了模拟信号源和定制DDS信号源的缺陷。基于FPGA的信号源只要增加频率控制字长,扩展波形数据,即可方便地实现频率的高分辨率和大范围可调的多种波形发生器,且不会影响信号源的可靠性及增加成本。实验证明该信号源波形频率、相位、幅值可方便、灵活调节,波形质量好,分辨率高。

参考文献:

[1] 晏勇.基于FPGA三相正弦信号发生器的设计与实现[J].电气自动化,2014,36(4):38-40.

[2] 杨大伟,杨秀芳,陈剑虹.基于FPGA的DDS多信号发生器的设计与实现[J].西安理工大学学报,2013,29(4):439-443.

[3] 吴征,苏淑靖.基于FPGA+PWM的多路信号发生器设计[J].电子技术应用,2014,40(3):38-40.

[4] 张兴红,蔡伟,邱磊,等.基于FPGA与DDS技术的可调超声波驱动电源设计[J].仪表技术与传感器,2015(6):84-87.

[5] 张林行,尚小虎,赵美聪,等.基于FPGA的直接数字合成信号源设计[J].电子设计工程,2016(1):172-174.

[6] 潘松,黄继业.EDA技术与VHDL[M].3版.北京:清华大学出版社,2009:94-148.

[7] PALNITKAR S.Verilog HDL数字设计与综合[M].夏宇闻,胡燕祥,刁岚松,译.北京:电子工业出版社,2009.

[8] 王海华.逻辑分析仪SignalTap Ⅱ在系统级调试中的应用[J].单片机与嵌入式系统应用,2011(2):11-14.

FU Yang

(College of Computer and Information Engineering, Beijing Technology and Business University,Beijing 100048, China)

Abstract:In order to solve problems of low precision and small frequency range of analog signal sources and unability to satisfy system requirement of bespoke direct digital frequency synthesis signal sources on aspects of control mode and frequency setting, a signal source based on FPGA was designed. The source is based on direct digital frequency synthesis principle, it adopts modularization design of FPGA and can output sine wave, square wave and triangular wave with adjustable frequency, phase and amplitude. The experimental results show that the signal has perfect quality of output wave, high frequency resolution and convenient control.

Key words:signal source; field-programmable gate array; direct digital frequency synthesis

文章编号:1671-251X(2016)07-0059-04

DOI:10.13272/j.issn.1671-251x.2016.07.014

收稿日期:2016-03-10;修回日期:2016-05-20;责任编辑:李明。

基金项目:北京市自然科学基金资助项目(4122020)。

作者简介:付扬(1962-),女,辽宁抚顺人,副教授,硕士,主要研究方向为电子技术应用、嵌入式片上系统设计及多媒体信息处理,E-mail:fsfy988@126.com。

中图分类号:TD67

文献标志码:A 网络出版时间:2016-07-05 15:02

付扬.基于FPGA的信号源设计[J].工矿自动化,2016,42(7):59-62.