文章编号:1671-251X(2014)01-0059-04 DOI:10.13272/j.issn.1671-251x.2014.01.016

范亚萍,王晓迎,李世银,等. 基于 Simulink 的数字下变频系统的设计与仿真[J]. 工矿自动化,2014,40(1): 59-62.

# 基于 Simulink 的数字下变频系统的设计与仿真

范亚萍, 王晓迎, 李世银, 邓超

(中国矿业大学 信息与电气工程学院, 江苏 徐州 221008)

**摘要:**针对数字下变频中低通抽取滤波器通带失真大、资源消耗严重等问题,采用锐化技术和二阶多项式插值补偿滤波器设计了基于 Simulink 的数字下变频系统,并利用 Simulink 构建系统模型。仿真结果表明,该系统不仅可以达到降低信号频率和速率的目的,同时可以有效改善抽取滤波器的通带与阻带特性,并减少了系统工作量。

**关键词:**数字下变频; 锐化技术; ISOP 滤波器; 直接数字频率合成器; 高速率抽取滤波; Simulink

中图分类号:TD655 文献标志码:A 网络出版时间:2013-12-31 09:32

网络出版地址:<http://www.cnki.net/kcms/doi/10.13272/j.issn.1671-251x.2014.01.016.html>

Design and simulation of digital down conversion system based on Simulink

FAN Yaping, WANG Xiaoying, LI Shiyin, DENG Chao

(School of Information and Electrical Engineering, China University of Mining and Technology,

Xuzhou 221008, China)

**Abstract:** In view of problem that low-pass decimation filter has big passband distortion and serious resource consumption in existing digital down conversion system, a digital down conversion system based on Simulink was designed adopting sharpening technique and interpolated second-order polynomial interpolation compensation filter, and system model was built by Simulink. The simulation results show that the system not only can reduce frequency and rate of signal, but also can effectively improve characteristics of decimation filter passband and stopband, and reduce workload of the system.

**Key words:** digital down conversion; sharpening technique; ISOP filter; direct digital synthesizer; high-rate decimation filter; Simulink

FIR

## 0 引言

随着矿井信息化、智能化的发展,软件无线电技术在现代煤矿通信中得到了广泛应用。在软件无线电框架下,为了解决高速 A/D 与 DSP 处理能力之间的矛盾,数字下变频(Digital Down Conversion, DDC)应运而生<sup>[1]</sup>。DDC 可以降低接收信号速率,实现中频信号与基带信号之间的转换,并对信号进行滤波。因此,当煤矿通信仪器接收到高速率信号时,可利用 DDC 来降低信号速率,滤除信号中的噪

声,这对仪器接收信号的后期处理具有重要作用。

传统的数字下变频系统存在低通抽取滤波器通带失真大、资源消耗严重等问题。针对这些问题,本文利用锐化技术和二阶多项式插值补偿(Interpolated Second-order Polynomial, ISOP)滤波器设计 DDC 系统,同时为了减少锐化滤波器的资源消耗,使用带有固定系数的有限脉冲响应(Finite Impulse Response, FIR)滤波器作为其第二级滤波,并进行了 Simulink 仿真验证。

收稿日期:2013-06-28;修回日期:2013-10-29。

作者简介:范亚萍(1987-),女,河南登封人,硕士研究生,主要研究方向为煤矿井下通信、软件无线电,E-mail:fanyaping87@126.com。

## 1 系统整体设计

DDC 主要包括混频、高速率抽取滤波 2 个模块,其中高速率抽取滤波器是运算量最大,也是对系统性能影响最大的部分。自 Hogenauer 提出 CIC (Cascade Integrator Comb) 滤波器后<sup>[2]</sup>,CIC 经常被用在 DDC 系统中充当高速率抽取滤波器。自此,数字下变频的一些研究工作开始围绕着 CIC 进行。其中,锐化滤波器(Sharpening CIC, SCIC)以增加计算量为代价,同时改善 CIC 滤波器的通带特性和其阻带特性;ISOP 滤波器可以有效地补偿 CIC 的通带衰减<sup>[3]</sup>。

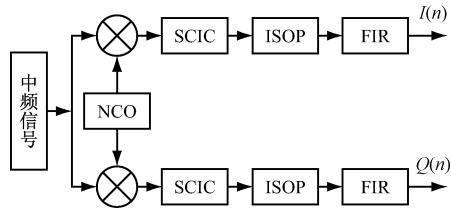

多通道数字下变频系统结构如图 1 所示。

图 1 多通道数字下变频系统结构

中频信号与数字振荡器 NCO (Numerically Controlled Oscillator)产生的本振信号进行混频,完成频谱搬移;再由 SCIC\_ISOP 滤波器经多倍抽取,降低信号速率;最后经低通滤波器滤除带外噪声,输出所需基带信号。系统在实现频谱搬移的同时,降低了信号的传输速率。

## 2 系统功能模块设计

### 2.1 混频模块的实现

采用直接数字频率合成器(Direct Digital Synthesizer, DDS)设计混频模块。在通信系统中,DDS 可以在基本不增加硬件成本的前提下,产生 2 路完全正交的正余弦单频信号<sup>[1]</sup>。

$$f_{\text{out}} = \frac{\Delta\theta}{2^N} f_{\text{clock}} \quad (1)$$

式中: $f_{\text{out}}$  为系统输出信号频率; $f_{\text{clock}}$  为 DDS 的工作时钟频率; $\Delta\theta$  为相位增量; $N$  为相位累加器的位数。

系统输出频率分辨率为

$$f_{\text{ref}} = \frac{1}{2^N} f_{\text{clock}} \quad (2)$$

由式(1)、式(2)可知,只需知道输入信号的频率和采样率,就可以按照系统的输出信号频率要求设置相应的 DDS 参数。

### 2.2 SCIC 滤波器设计

CIC 滤波器因不含乘法运算,处理速度快,往往

被用在采样速率较高的场合<sup>[1]</sup>。单级 CIC 的阻带衰减比较差,多级级联虽然可以增大阻带衰减,但会带来带内衰减过大的问题。

利用锐化技术所得的滤波器通常称为 SCIC 滤波器。SCIC 既能增加 CIC 阻带衰减,又能补偿带内衰减。SCIC 传递函数为

$$H_S = 3z^{-\frac{N}{2}(D-1)} H_{\text{CIC}}^2(z) - 2H_{\text{CIC}}^3(z) \quad (3)$$

式中: $N$  为 SCIC 的级联阶数; $D$  为抽取倍数; $\frac{N}{2}(D-1)$  为滤波器延迟; $H_{\text{CIC}}$  为 CIC 滤波器的传递函数。

为了可以利用第一恒等变换使得群延迟的均衡与  $D$  无关, $N$  应为偶数。SCIC 传递函数的归一化频率响应为

$$H_S[\exp(j\omega)] = 3 \left[ DSa\left(\frac{\omega D}{2}\right) Sa^{-1}\left(\frac{\omega}{2}\right) \right]^{10} - 2 \left[ DSa\left(\frac{\omega D}{2}\right) Sa^{-1}\left(\frac{\omega}{2}\right) \right]^{15} \quad (4)$$

式中: $Sa = (\sin t)/t$ 。

由式(3)、式(4)可知,SCIC 比 CIC 多 2 个积分器和 2 个梳状部分,消耗的资源约为 CIC 的 3 倍。为了使 SCIC 滤波器实现资源的节约,可使用带有固定系数的第二级滤波。本文采用 FIR 数字滤波器作为 SCIC 的第二级滤波器。

### 2.3 ISOP 滤波器设计

在多倍抽取后,SCIC 通带下降会导致部分有用信号衰减,为了补偿带内容差,在 SCIC 之后级联 ISOP 滤波器。其转移函数为<sup>[3]</sup>

$$H_1(z) = \frac{1}{|c+2|} (1 + cz^{-I} + z^{-2I}) \quad (5)$$

式中: $I, c$  为 ISOP 滤波器的 2 个可控参数。

ISOP 的幅频特性为<sup>[3]</sup>

$$|H_1[\exp(j\omega)]| = \frac{1}{|c+2|} |c + 2\cos(I\omega)| \quad (6)$$

由 ISOP 滤波器的幅频特性可知:当  $c < -2$  时,ISOP 滤波器在区间  $\omega \in [0, \pi/I]$  内是单调递增的,此范围应与有效信号带宽  $\omega = 2\pi f_b$  保持一致。令  $I = kD$ ,由通带最小原则可得  $k$  要满足以下条件:

$$1 \leq k \leq [1/2Df_b] \quad (7)$$

$$|H[\exp(j\omega)]H_1[\exp(j\omega)] - 1| < \delta,$$

$$0 \leq \omega \leq 2\pi f_b \quad (8)$$

式中: $f_b$  为归一化通带带宽,令  $f_b = 250/40\ 000 = 0.006\ 3$ 。

由式(7)、式(8)可以得到一组  $(k, c)$  使  $\delta$  达到最小。

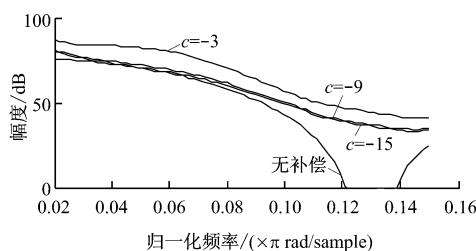

图2为 $k=1$ 和 $c$ 分别为 $-3, -9, -15$ 与无补偿时的ISOP的补偿情况。由图2可知,当 $c=-9$ 时,补偿效果较好。

图2 ISOP滤波器的补偿特性

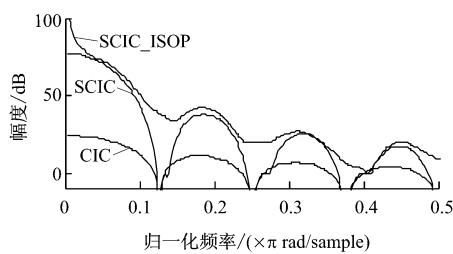

令 $D=16, c=-9$ ,将SCIC\_ISOP、SCIC与CIC在16倍抽取后的频谱进行比较,如图3所示。由图3可知,SCIC\_ISOP滤波器的阻带特性与CIC滤波器相比有很大的改进,通带特性与SCIC相比也得到了补偿,有效地加宽了通带。

图3 SCIC-ISOP、SCIC、CIC频谱

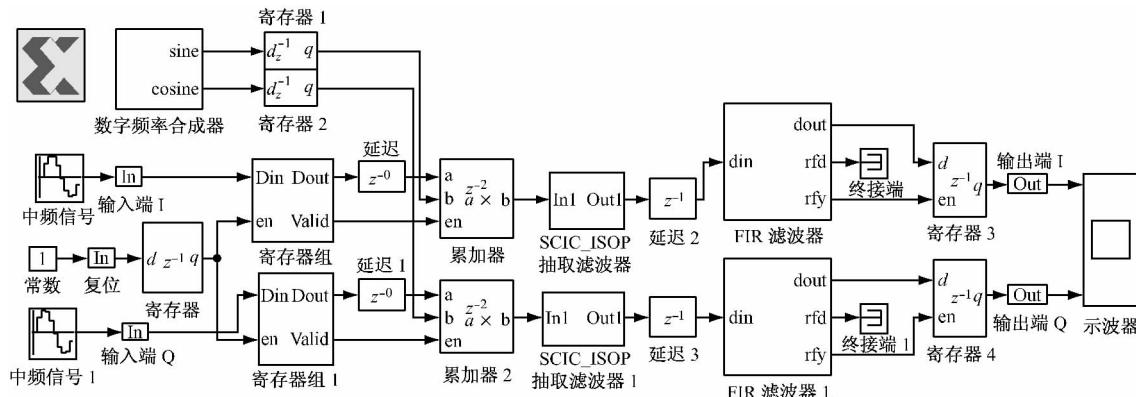

图4 数字下变频系统模型

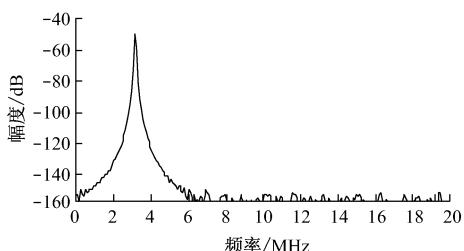

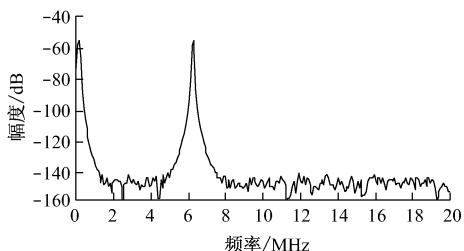

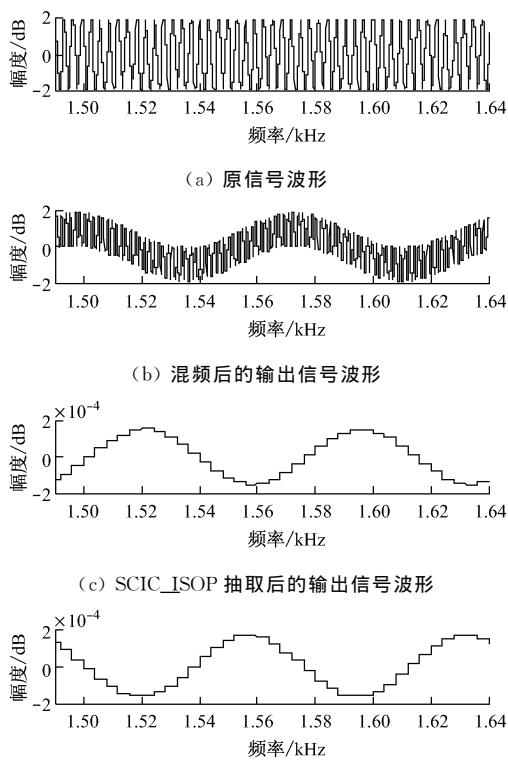

图5为输入中频信号频谱图,图6为混频后信号频谱图。由图5可知,输入中频信号的中心频率为3.2 MHz。对比图5和图6可知,设计的混频模块已将信号频谱搬移到了中心频率为0 Hz附近,实现了信号下变频的基本功能。

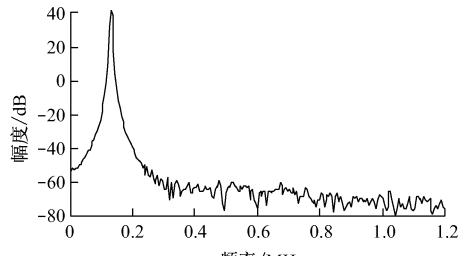

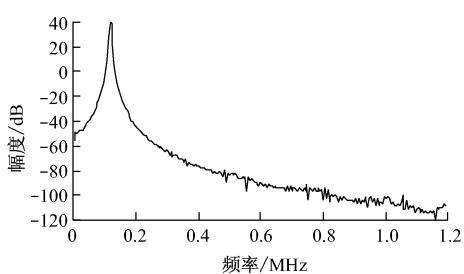

图7为SCIC\_ISOP抽取后的信号频谱图,图8为滤波后输出信号频谱图。由图7和图8可知,FIR滤波器对抽取后信号进行低通滤波,基本可以

#### 2.4 FIR滤波器设计

FIR滤波器可以进一步补偿SCIC\_ISOP的带内波纹和阻带衰减,滤除信号噪声,同时使SCIC实现资源的节约。利用Simulink工具箱中的FDATool,同时采用凯撒窗来设计FIR滤波器。在确定滤波器的结构后,根据系统对滤波器的性能指标要求,可以确定滤波器系数。

#### 3 系统测试

中频信号可以在一定程度上穿透煤层和岩层传播,因此,井下通信系统大多工作在中频段,所以实际应用中需采用数字下变频系统降低信号频率,方便仪器对信号的后期处理。

根据实际要求,Simulink产生采样率为40 MHz的中频信号。信号分为I、Q两路16位信号输入,经混频、16倍的抽取滤波和低通滤波,输出采样速率为2.5 MHz、带宽为250 kHz的基带信号。

本次测试所需软件System Generator是Matlab/Simulink环境下的一个工具箱,利用该软件可以进行模型式的设计方法,方便直观。仿真过程中数据由Simulink提供,测试结果可以通过示波器和输出端观察。按照上述模块的设计和理论分析,通过建模,对所设计的数字下变频系统进行仿真测试。系统模型如图4所示。

滤除0.2 MHz以外的带内干扰信号,从而获得更准确的信号。

图9为系统输出信号的时域波形图。由图9可以看出,处理后的信号速率已大为降低,一些噪声已被滤除,输出的波形更加精确。

表1为在处理相同信号时,包含不同抽取滤波器的系统仿真所需的时间对比表。由表1可知,SCIC\_ISOP和CIC\_ISOP资源消耗相差不大,表明

图5 输入中频信号频谱

图6 混频后信号频谱

图7 SCIC\_ISOP 抽取后的信号频谱

图8 滤波后输出信号频谱

设计的数字下变频系统既有效地克服了 SCIC 结构复杂、资源消耗大的缺点,又充分发挥了其增加阻带衰减、补偿带内衰减的优点。

表1 CIC\_ISOP 和 SCIC\_ISOP 系统仿真所需时间 ms

| 滤波器       | 编译时间   | 仿真时间   | 总时间    |

|-----------|--------|--------|--------|

| CIC_ISOP  | 11 752 | 75 292 | 77 044 |

| SCIC_ISOP | 1 263  | 80 285 | 81 548 |

由以上测试结果可知,利用 SCIC\_ISOP 滤波器来设计 DDC 系统,不仅可以达到降低信号频率和速率的目的,同时可以有效地改善抽取滤波器的通带与阻带特性,并减少了系统工作量。

图9 系统输出信号的时域波形对比

#### 4 结语

介绍了基于 Simulink 设计数字下变频系统的实现过程,并通过 System Generator 以图形的方式仿真验证了所设计的下变频系统的功能,避免了采用传统语言设计时的繁琐工作,减少了工作量,节约了成本。而且,在实际应用中只需确定输入中频信号和所需输出信号的频率和采样频率等基本参数,就可实现数字下变频功能,实用性强。

#### 参考文献:

- [1] 袁超伟,姜宇柏.软件无线电原理与工程应用[M].北京:机械工业出版社,2007.

- [2] HOGENAUER E. An economical class of digital filters for decimation and interpolation [J]. IEEE Transactions on Acoustics, Speech and Signal Processing, 1981, 29(2):155-162.

- [3] 叶和忠.软件无线电中数字上下变频器的研究与开发[D].桂林:桂林电子科技大学,2010.

- [4] 张维.基于 Simulink 的数字上下变频建模与仿真[J].数字通信工程应用,2011(1):92-95.

- [5] 徐小明,蔡灿辉.基于 FPGA 的数字下变频(DDC)设计[J].通信技术,2011,44(10):19-22.

- [6] 尹玉兴,刘振坚,项止武.基于 Matlab 的 FIR 数字滤波器设计与仿真[J].工矿自动化,2011,37(12):60-63.